Características principales

Tres funciones en un único dispositivo

- Programación por almacenamiento masivo (MSC): copie archivos

.bin/.hexpara grabar la Flash. - Puerto COM virtual (CDC): registre trazas y use una consola interactiva sin un adaptador USB‑UART adicional.

- Depuración CMSIS‑DAP: actúa como una sonda CMSIS‑DAP estándar con puntos de ruptura y acceso a memoria.

Hardware fácil de integrar

- USB‑C como único conector hacia el PC: alimentación y datos SWD/JTAG en un solo cable.

- Cabeceras en el borde de la placa para enrutar SWD y UART a sus propias placas base.

- Regulación y protección integradas, adecuadas para objetivos típicos de 3,3 V Cortex‑M.

Ecosistema abierto · estándar CMSIS‑DAP

- Basado en el proyecto de código abierto Arm Mbed DAPLink.

- Protocolo CMSIS‑DAP estándar, sin atarse a un único proveedor de MCU.

- El firmware de la interfaz se puede recompilar para admitir más objetivos o funciones personalizadas.

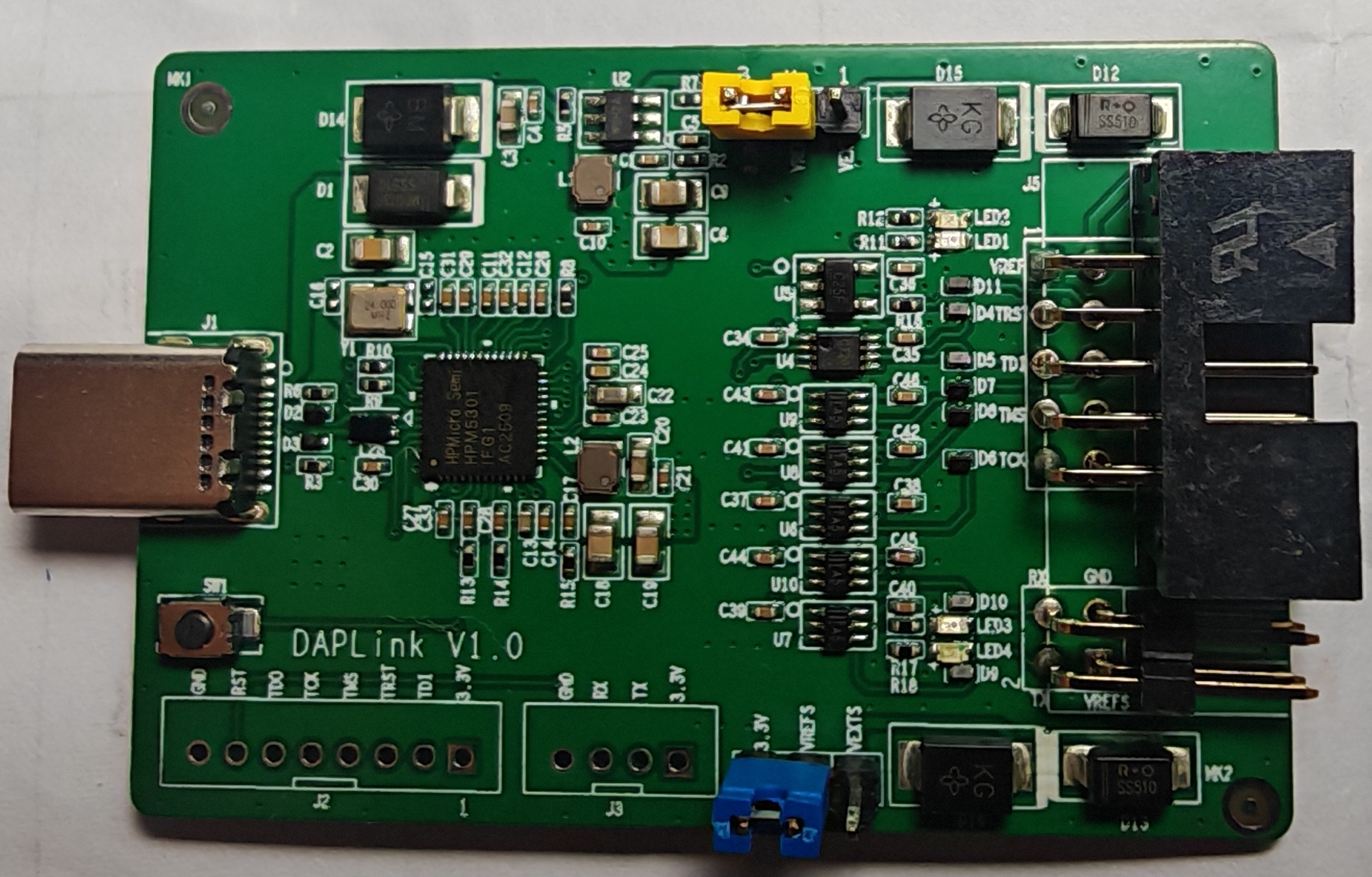

Descripción de hardware

| Elemento | Detalles |

|---|---|

| MCU de interfaz | MCU ARM Cortex‑M que ejecuta el firmware de interfaz DAPLink (clase LPC / STM32). |

| Conexión al PC | USB Tipo‑C; alimentación de 5 V y datos. |

| Interfaces hacia el objetivo | Cabecera de depuración SWD/JTAG + cabecera UART (TX/RX/GND, lógica de 3,3 V). |

| Alimentación | 5 V desde USB‑C, reguladores en la placa; pin VREF para detectar la tensión de E/S del objetivo (típicamente 2,3–3,3 V). |

| Indicadores | Varios LED para estado de depuración, monitorización de VREF y diagnóstico de alimentación. |

| Actualización de firmware | Botón en la placa para entrar en modo bootloader y actualizar el firmware de interfaz DAPLink cuando sea necesario. |

| Factor de forma | PCB compacto, listo para integrarse en una pequeña carcasa (ver render del chasis). |

Conectores y señales

Cabecera DEBUG (SWD / JTAG)

- Pines típicos: TCK/SWCLK, TMS/SWDIO, TDI, TDO, nRESET, VREF, GND.

- Usada para depuración en chip, programación de Flash y pruebas de producción.

Cabecera UART

- Señales: TX, RX, GND, 3,3 V.

- Actúa como puerto de consola del objetivo; ideal para registros de log y acceso a shell.

Botones / jumpers

- Botón para entrar en el bootloader o reiniciar la MCU de interfaz (según el firmware).

- Jumpers para configurar la alimentación del objetivo o el modo de funcionamiento, según el diseño final de la PCB.

Inicio rápido

1

Conectar el hardware

- Conecte DAP‑LINK al PC mediante un cable USB‑C.

- Conecte la cabecera DEBUG al conector SWD/JTAG de la placa objetivo y, si es necesario, conecte también la UART.

- Asegúrese de que la alimentación y la tensión VREF del objetivo (normalmente 3,3 V) coinciden.

2

Programación drag‑and‑drop

- En el PC aparecerá una nueva unidad USB (el nombre depende del firmware).

- Copie el archivo

.bin/.hexcompilado a esa unidad. - DAP‑LINK programará automáticamente la memoria Flash del MCU objetivo.

3

Registro serie y depuración

- Se expondrá un puerto COM virtual; ábralo con su terminal favorito para ver logs.

- En Keil / pyOCD / OpenOCD seleccione el dispositivo CMSIS‑DAP y comience la depuración a nivel de código fuente.

FAQ

¿Qué herramientas son compatibles?

Cualquier depurador que hable CMSIS‑DAP: Keil MDK, Arm DS, pyOCD, algunas configuraciones de OpenOCD y entornos de VS Code que usen backends CMSIS‑DAP.

¿En qué se diferencia de ST‑LINK / J‑LINK?

DAP‑LINK se basa en el proyecto abierto DAPLink y el protocolo estándar CMSIS‑DAP, por lo que no queda limitado al ecosistema de un solo proveedor. Es un buen cabezal de depuración genérico para sus propias placas o líneas de producto.

¿Puedo personalizar o sustituir el firmware?

Sí. La MCU de interfaz puede actualizarse con diferentes builds de DAPLink para admitir nuevos objetivos o añadir funciones específicas.