ฟีเจอร์หลัก

สามฟังก์ชันในเครื่องเดียว

- การแฟลชผ่าน Mass Storage (MSC) – คัดลอกไฟล์

.bin/.hexเพื่อเขียนลง Flash - พอร์ต COM เสมือน (CDC) – แสดง log และคอนโซลแบบโต้ตอบได้โดยไม่ต้องใช้ USB‑UART แยกต่างหาก

- ดีบักแบบ CMSIS‑DAP – ทำงานเป็นโปรบ CMSIS‑DAP มาตรฐาน รองรับ breakpoint และการเข้าถึงหน่วยความจำ

ฮาร์ดแวร์ออกแบบมาให้ง่ายต่อการฝัง

- ใช้ USB‑C เป็นคอนเนกเตอร์ฝั่งพีซีเพียงพอร์ตเดียว – ส่งทั้งไฟเลี้ยงและข้อมูล SWD/JTAG ในสายเดียว

- หัวแถวที่ขอบบอร์ดช่วยให้ต่อสาย SWD และ UART ไปยังเมนบอร์ดของคุณได้สะดวก

- วงจรจ่ายไฟและป้องกันในตัว รองรับบอร์ดเป้าหมาย Cortex‑M 3.3 V ส่วนใหญ่ได้โดยตรง

ระบบนิเวศแบบเปิด · มาตรฐาน CMSIS‑DAP

- พัฒนาบนโปรเจกต์โอเพนซอร์ส Arm Mbed DAPLink

- ใช้โปรโตคอล CMSIS‑DAP มาตรฐาน ไม่ผูกกับผู้ผลิต MCU รายใดรายหนึ่ง

- เฟิร์มแวร์ส่วนอินเทอร์เฟซสามารถคอมไพล์ใหม่เพื่อรองรับเป้าหมายหรือฟีเจอร์เพิ่มเติมตามต้องการ

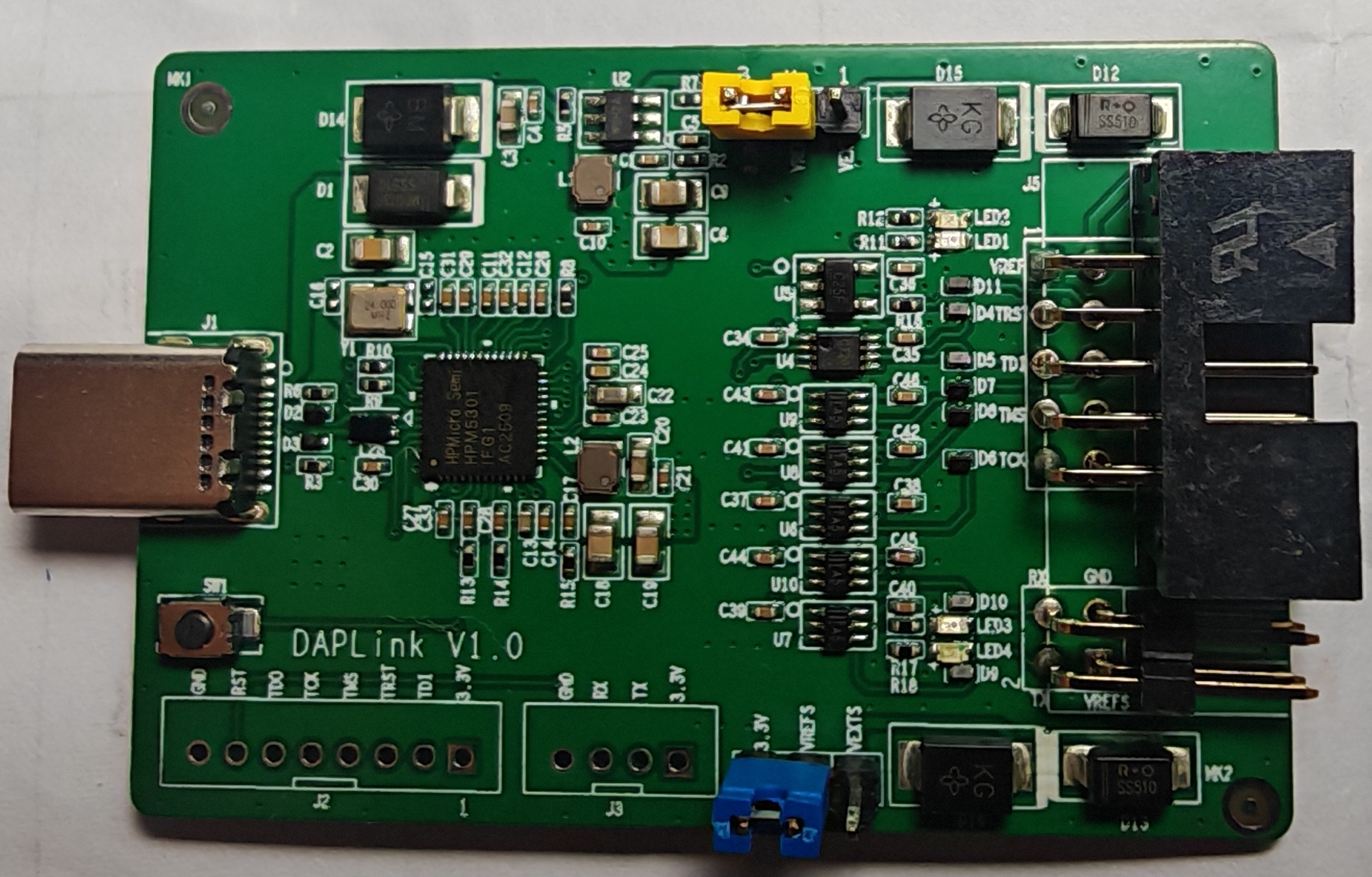

ภาพรวมฮาร์ดแวร์

| หัวข้อ | รายละเอียด |

|---|---|

| MCU ฝั่งอินเทอร์เฟซ | MCU ARM Cortex‑M ที่รันเฟิร์มแวร์อินเทอร์เฟซ DAPLink (ระดับ LPC / STM32) |

| การเชื่อมต่อกับพีซี | USB Type‑C; จ่ายไฟ 5 V และรับ‑ส่งข้อมูล |

| อินเทอร์เฟซไปยังเป้าหมาย | หัวแถวดีบัก SWD/JTAG + หัวแถว UART (TX/RX/GND, ลอจิก 3.3 V) |

| แหล่งจ่ายไฟ | รับ 5 V จาก USB‑C มีวงจรเรกูเลตในบอร์ด; ขา VREF ใช้ตรวจระดับแรงดัน I/O ของเป้าหมาย (ประมาณ 2.3–3.3 V) |

| ตัวแสดงสถานะ | LED หลายดวงสำหรับสถานะดีบัก การเฝ้าดู VREF และการวิเคราะห์ปัญหาด้านพลังงาน |

| อัปเดตเฟิร์มแวร์ | ปุ่มบนบอร์ดสำหรับเข้าสู่โหมด bootloader – ใช้อัปเดตเฟิร์มแวร์อินเทอร์เฟซ DAPLink เมื่อจำเป็น |

| ขนาดและรูปทรง | PCB ขนาดกะทัดรัด พร้อมติดตั้งในเคสขนาดเล็ก (ตามตัวอย่างเรนเดอร์) |

คอนเนกเตอร์และสัญญาณ

หัวแถว DEBUG (SWD / JTAG)

- ขาทั่วไป: TCK/SWCLK, TMS/SWDIO, TDI, TDO, nRESET, VREF, GND

- ใช้สำหรับดีบักบนชิป การแฟลช และการทดสอบในสายการผลิต

หัวแถว UART

- สัญญาณ: TX, RX, GND, 3.3 V

- ทำหน้าที่เป็นพอร์ตคอนโซลของบอร์ดเป้าหมาย เหมาะสำหรับแสดง log และสั่งงานผ่าน shell

ปุ่ม / จัมเปอร์

- ปุ่มใช้เข้าสู่ bootloader หรือรีเซ็ต MCU ฝั่งอินเทอร์เฟซ (พฤติกรรมขึ้นอยู่กับเฟิร์มแวร์)

- จัมเปอร์ใช้กำหนดว่าจะจ่ายไฟให้บอร์ดเป้าหมายหรือเลือกโหมดการทำงาน ตามดีไซน์ PCB สุดท้าย

เริ่มต้นอย่างรวดเร็ว

1

เชื่อมต่อฮาร์ดแวร์

- เชื่อมต่อ DAP‑LINK กับพีซีด้วยสาย USB‑C

- ต่อหัวแถว DEBUG เข้ากับหัวแถว SWD/JTAG บนบอร์ดเป้าหมาย และหากต้องใช้ UART ให้ต่อหัวแถวนั้นเพิ่ม

- ตรวจสอบให้แน่ใจว่าแรงดันเลี้ยงและ VREF ของเป้าหมาย (โดยมาก 3.3 V) ถูกต้อง

2

แฟลชแบบลาก‑แล้ว‑วาง

- พีซีจะแสดงไดรฟ์ USB ใหม่ (ชื่อไดรฟ์ขึ้นอยู่กับเวอร์ชันเฟิร์มแวร์)

- คัดลอกไฟล์

.bin/.hexที่คอมไพล์แล้วลงในไดรฟ์นี้ - DAP‑LINK จะเขียนเฟิร์มแวร์ลง Flash ของ MCU เป้าหมายโดยอัตโนมัติ

3

Log แบบอนุกรมและการดีบัก

- จะมีพอร์ต COM เสมือนปรากฏขึ้น – เปิดด้วยโปรแกรมเทอร์มินัลที่คุณใช้เพื่อดู log

- ใน Keil / pyOCD / OpenOCD ให้เลือกอุปกรณ์ CMSIS‑DAP แล้วเริ่มดีบักในระดับซอร์สโค้ด

คำถามที่พบบ่อย (FAQ)

รองรับเครื่องมือใดบ้าง?

รองรับดีบักเกอร์ที่ใช้ CMSIS‑DAP เช่น Keil MDK, Arm DS, pyOCD, การตั้งค่า OpenOCD บางแบบ และสภาพแวดล้อม VS Code ที่ใช้ backend แบบ CMSIS‑DAP

ต่างจาก ST‑LINK / J‑LINK อย่างไร?

DAP‑LINK พัฒนาบนโปรเจกต์โอเพนซอร์ส DAPLink และโปรโตคอลมาตรฐาน CMSIS‑DAP จึงไม่ถูกผูกกับระบบนิเวศของผู้ผลิตรายเดียว เหมาะสำหรับใช้เป็นหัวดีบักแบบทั่วไปกับบอร์ดและผลิตภัณฑ์ของคุณเอง

สามารถปรับแต่งหรือเปลี่ยนเฟิร์มแวร์ได้หรือไม่?

ได้ MCU ฝั่งอินเทอร์เฟซสามารถอัปเดตด้วย build ของ DAPLink ที่ต่างกัน เพื่อรองรับบอร์ดเป้าหมายใหม่ ๆ หรือเพิ่มฟีเจอร์พิเศษตามต้องการ