Ciri utama

Tiga fungsi dalam satu peranti

- Pemprograman Mass Storage (MSC) – salin fail

.bin/.hexuntuk memprogram Flash. - Port COM maya (CDC) – log dan konsol interaktif tanpa penyesuai USB‑UART berasingan.

- Nyahpepijat CMSIS‑DAP – bertindak sebagai probe CMSIS‑DAP piawai untuk breakpoint dan akses memori.

Perkakasan mudah diintegrasi

- USB‑C sebagai satu‑satunya penyambung hos – bekalan kuasa dan data SWD/JTAG dalam satu kabel.

- Header di tepi papan membolehkan anda membawa isyarat SWD dan UART ke papan utama anda.

- Regulasi dan perlindungan on‑board yang sesuai untuk kebanyakan sasaran Cortex‑M 3.3 V.

Ekosistem terbuka · standard CMSIS‑DAP

- Dibina di atas projek sumber terbuka Arm Mbed DAPLink.

- Protokol CMSIS‑DAP piawai, tidak terikat kepada satu pengeluar MCU sahaja.

- Firmware antara muka boleh dikompil semula untuk menyokong lebih banyak sasaran atau ciri tersuai.

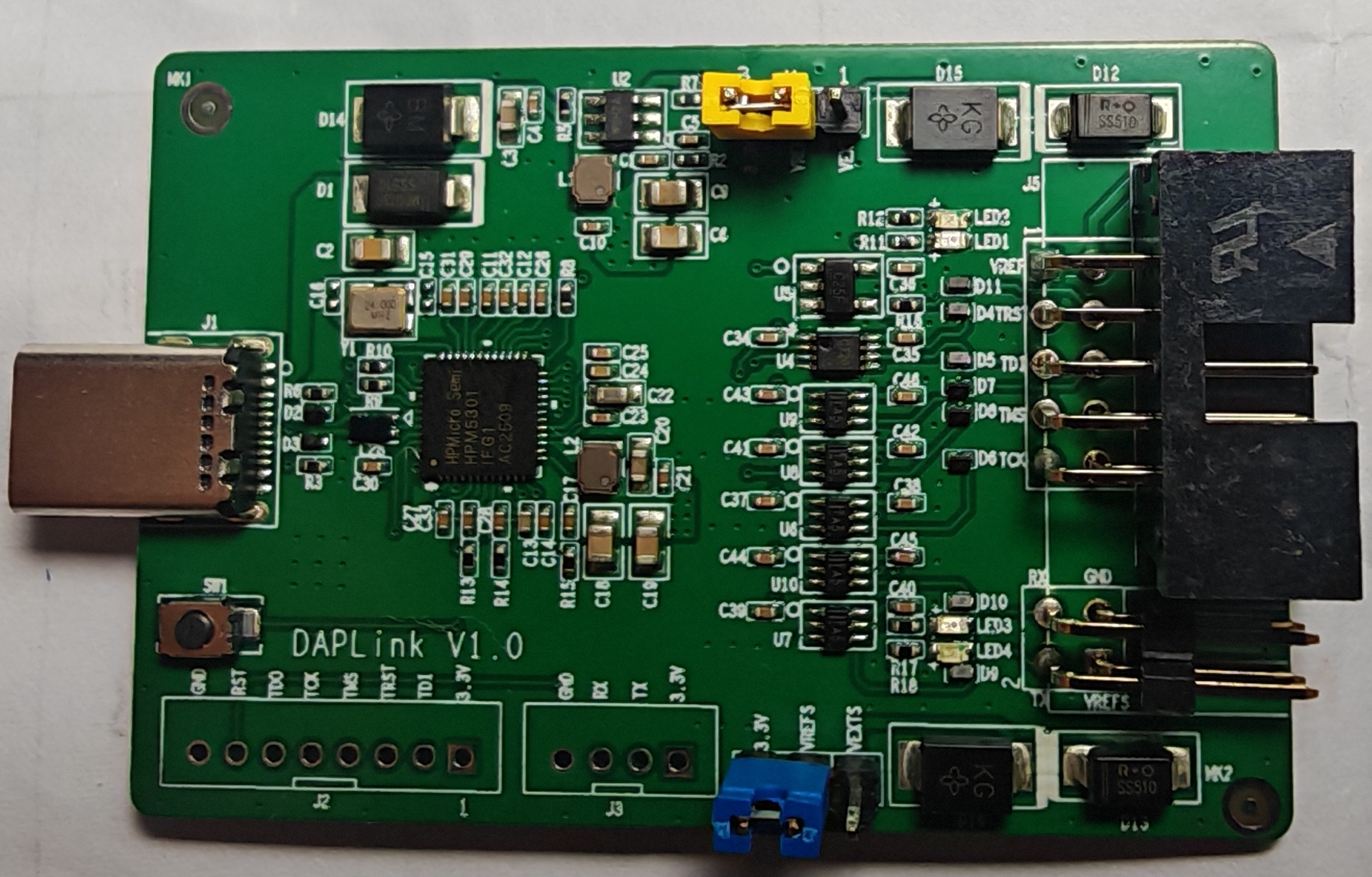

Gambaran keseluruhan perkakasan

| Item | Butiran |

|---|---|

| MCU antara muka | MCU ARM Cortex‑M yang menjalankan firmware antara muka DAPLink (kelas LPC / STM32). |

| Sambungan ke PC | USB Type‑C; bekalan kuasa 5 V dan data. |

| Antara muka ke sasaran | Header debug SWD/JTAG + header UART (TX/RX/GND, logik 3.3 V). |

| Bekalan kuasa | 5 V daripada USB‑C, regulator pada papan; pin VREF untuk mengesan voltan I/O sasaran (biasanya 2.3–3.3 V). |

| Penunjuk | Beberapa LED untuk status debug, pemantauan VREF dan diagnostik kuasa. |

| Kemas kini firmware | Butang pada papan untuk masuk ke mod bootloader – kemas kini firmware antara muka DAPLink apabila perlu. |

| Form factor | PCB padat, sedia dipasang ke dalam sarung kecil (lihat render sarung). |

Penyambung & isyarat

Header DEBUG (SWD / JTAG)

- Pins biasa: TCK/SWCLK, TMS/SWDIO, TDI, TDO, nRESET, VREF, GND.

- Digunakan untuk nyahpepijat on‑chip, pemprograman Flash dan ujian pengeluaran.

Header UART

- Isyarat: TX, RX, GND, 3.3 V.

- Bertindak sebagai port konsol sasaran – sesuai untuk log dan akses shell.

Butang / jumper

- Butang untuk masuk ke mod bootloader atau menetapkan semula MCU antara muka (bergantung pada firmware).

- Jumper untuk mengkonfigurasi bekalan kuasa sasaran atau mod operasi, mengikut reka bentuk akhir PCB.

Mulakan dengan pantas

1

Sambungkan perkakasan

- Sambungkan DAP‑LINK ke PC menggunakan kabel USB‑C.

- Sambungkan header DEBUG ke header SWD/JTAG pada papan sasaran dan, jika perlu, sambungkan juga UART.

- Pastikan bekalan kuasa dan voltan VREF sasaran (biasanya 3.3 V) adalah betul.

2

Flash seret‑dan‑lepas

- Sebuah pemacu USB baharu akan muncul pada PC (nama bergantung pada build firmware).

- Salin fail

.bin/.hexyang telah disusun ke pemacu tersebut. - DAP‑LINK akan memprogram Flash MCU sasaran secara automatik.

3

Log bersiri & nyahpepijat

- Port COM maya akan terdedah – buka dengan aplikasi terminal kegemaran anda untuk melihat log.

- Dalam Keil / pyOCD / OpenOCD, pilih peranti CMSIS‑DAP dan mula nyahpepijat pada aras kod sumber.

Soalan lazim (FAQ)

Alat manakah yang disokong?

Mana‑mana debugger yang menyokong CMSIS‑DAP: Keil MDK, Arm DS, pyOCD, beberapa konfigurasi OpenOCD dan persekitaran VS Code dengan backend CMSIS‑DAP.

Apakah perbezaan berbanding ST‑LINK / J‑LINK?

DAP‑LINK dibina di atas projek sumber terbuka DAPLink dan protokol CMSIS‑DAP piawai, jadi ia tidak terkunci kepada ekosistem satu pembekal sahaja. Sesuai digunakan sebagai kepala debug generik untuk papan dan produk anda.

Bolehkah saya menyesuaikan atau menukar firmware?

Boleh. MCU antara muka boleh dikemas kini dengan build DAPLink yang berbeza bagi menyokong sasaran baharu atau menambah ciri khusus.